# = Preliminary =

ASAHI KASEI EMD

Asahi **KASEI**

## 96kHz 24-Bit $\Delta\Sigma$ ADC with 0V Bias Selector

#### GENERAL DESCRIPTION

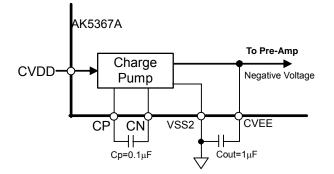

AK5367A is a high-performance 24-bit, 96kHz sampling ADC for consumer audio and digital recording applications. The AK5367A uses an Enhanced Dual-Bit modulator architecture, this analog-to-digital converter has an impressive dynamic range of 102dB with high level integration. The AK5367A has a 4-channel stereo input selector, an input Programmable Gain Amplifier with resistance. All this integration with high-performance makes the AK5367A well suited for CD and DVD recording systems. The integrated charge pump circuit can generate the negative power supply and remove the output coupling capacitor.

#### FEATURES

#### 1. 24bit Stereo ADC

- 4:1 0V Bias Stereo input Selector

- Digital HPF for offset cancellation (fc=1.0Hz@fs=48kHz)

- Decimation LPF: -0.2dB@ 20kHz, -3.0dB@23kHz (fs=48kHz)

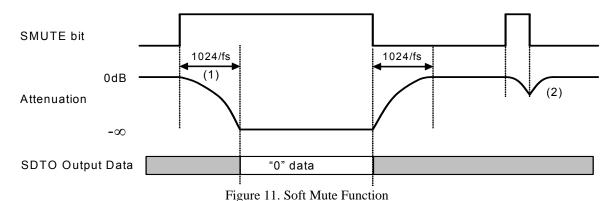

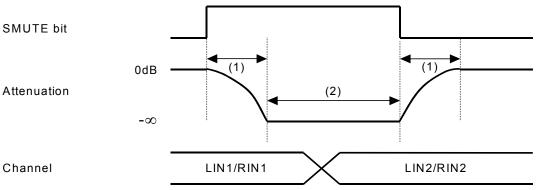

- Soft Mute

- Single-end Inputs

- S/(N+D): 90dB

- DR, S/N: 102dB

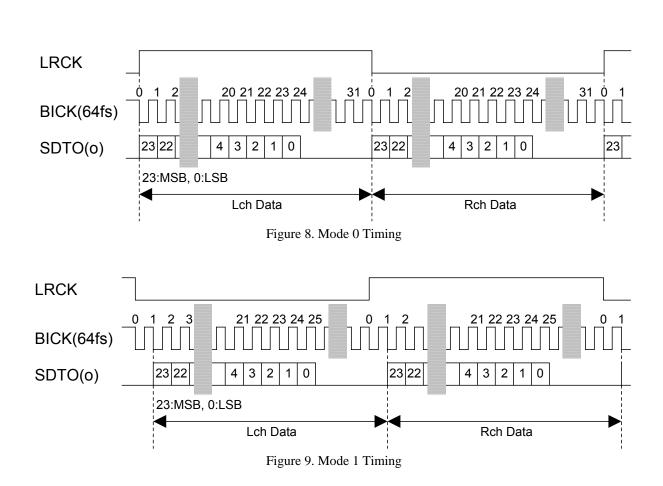

- Audio I/F Format: 24bit MSB justified, I<sup>2</sup>S

- 2. Control Interface: I<sup>2</sup>C-Bus

- 3. Master Mode / Slave Mode

- 4. Master Clock:

- 256fs/384fs (32kHz ~ 96kHz)

- 512fs/768fs (32kHz ~ 48kHz)

- 5. Sampling Rate: 32kHz to 96kHz

- 6. Power Supply

- Analog Supply: 4.5 ~ 5.5V

- Digital Supply: 3.0 ~ 3.6V

- 7. Ta = −20 ~ 85°C

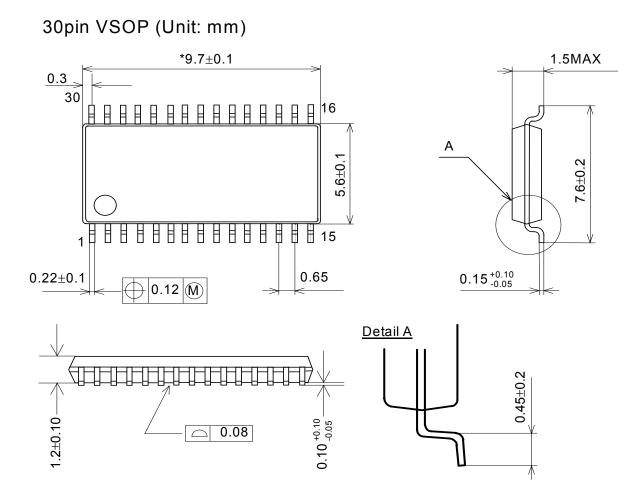

- 8. Package: 30pin VSOP

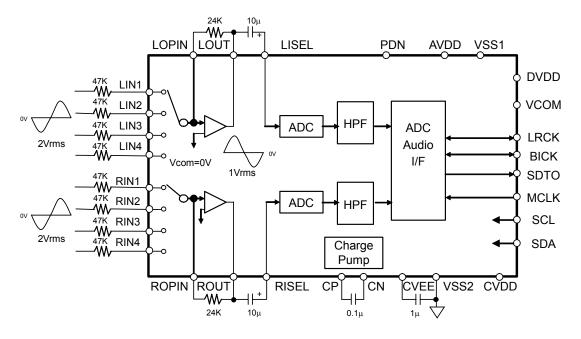

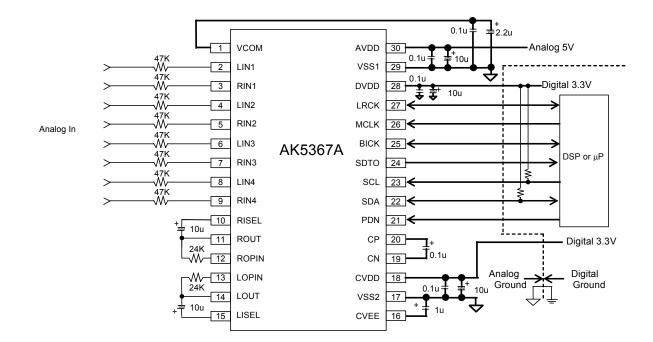

#### Block Diagram

Figure 1. AK5367A Block Diagram

## Ordering Guide

| AK5367AEF | $-20 \sim +85^{\circ}\mathrm{C}$ | 30pin VSOP (0.65mm pitch) |

|-----------|----------------------------------|---------------------------|

| AKD5367A  | Evaluation Board for AK536       | 57A                       |

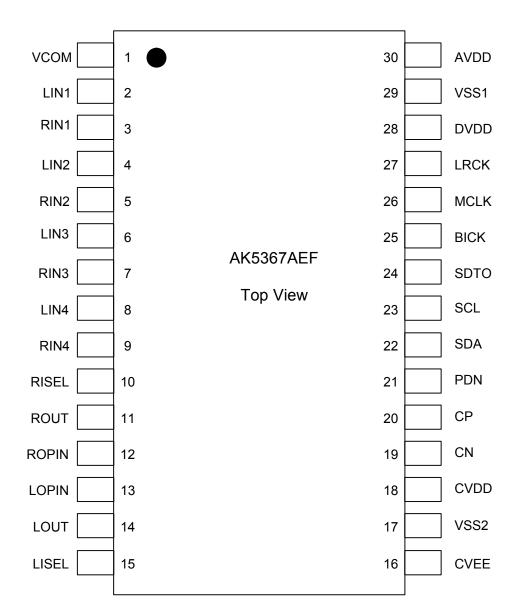

## Pin Layout

## **PIN/FUNCTION**

| No. | Pin Name | I/O | Function                                                                                                                                                                                                                                                                                                                 |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NCOM     |     | Common Voltage Output Pin, AVDD/2                                                                                                                                                                                                                                                                                        |

| 1   | VCOM     | 0   | Bias voltage of ADC input.                                                                                                                                                                                                                                                                                               |

| 2   | LIN1     | Ι   | Lch Analog Input 1 Pin                                                                                                                                                                                                                                                                                                   |

| 3   | RIN1     | Ι   | Rch Analog Input 1 Pin                                                                                                                                                                                                                                                                                                   |

| 4   | LIN2     | Ι   | Lch Analog Input 2 Pin                                                                                                                                                                                                                                                                                                   |

| 5   | RIN2     | Ι   | Rch Analog Input 2 Pin                                                                                                                                                                                                                                                                                                   |

| 6   | LIN3     | Ι   | Lch Analog Input 3 Pin                                                                                                                                                                                                                                                                                                   |

| 7   | RIN3     | Ι   | Rch Analog Input 3 Pin                                                                                                                                                                                                                                                                                                   |

| 8   | LIN4     | Ι   | Lch Analog Input 4 Pin                                                                                                                                                                                                                                                                                                   |

| 9   | RIN4     | Ι   | Rch Analog Input 4 Pin                                                                                                                                                                                                                                                                                                   |

| 10  | RISEL    | Ι   | Rch Analog Input Pin                                                                                                                                                                                                                                                                                                     |

| 11  | ROUT     | 0   | Rch Feedback Resistor Output Pin                                                                                                                                                                                                                                                                                         |

| 12  | ROPIN    | 0   | Rch Feedback Resistor Input Pin                                                                                                                                                                                                                                                                                          |

| 13  | LOPIN    | 0   | Lch Feedback Resistor Intput Pin                                                                                                                                                                                                                                                                                         |

| 14  | LOUT     | 0   | Lch Feedback Resistor Output Pin                                                                                                                                                                                                                                                                                         |

| 15  | LISEL    | Ι   | Lch Analog Input Pin                                                                                                                                                                                                                                                                                                     |

| 16  | CVEE     | 0   | Negative Voltage Output Pin<br>Connect to VSS2 with a $1.0\mu$ F capacitor which is low ESR (Equivalent Series<br>Resistance) over all temperature range. When this capacitor has the polarity, the<br>positive polarity pin must be connected to the VSS2 pin. Non polarity capacitors<br>can also be used.             |

| 17  | VSS2     | -   | Charge Pump Ground Pin, $0V$<br>Connect to CVEE with a $1.0\mu$ F capacitor which is low ESR (Equivalent Series<br>Resistance) over all temperature range. When this capacitor has the polarity, the<br>positive polarity pin must be connected to the VSS2 pin. Non polarity capacitors<br>can also be used.            |

| 18  | CVDD     | -   | Charge Pump Power Supply Pin, 3.0V~3.6V                                                                                                                                                                                                                                                                                  |

| 19  | CN       | Ι   | Negative Charge Pump Capacitor Terminal Pin<br>Connect to CP with a $0.1\mu$ F capacitor which is low ESR (Equivalent Series<br>Resistance) over all temperature range. When this capacitor has the polarity, the<br>positive polarity pin must be connected to the CP pin. Non polarity capacitors can<br>also be used. |

| 20  | СР       | 0   | Positive Charge Pump Capacitor Terminal Pin<br>Connect to CN with a $0.1\mu$ F capacitor which is low ESR (Equivalent Series<br>Resistance) over all temperature range. When this capacitor has the polarity, the<br>positive polarity pin must be connected to the CP pin. Non polarity capacitors can<br>also be used. |

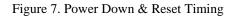

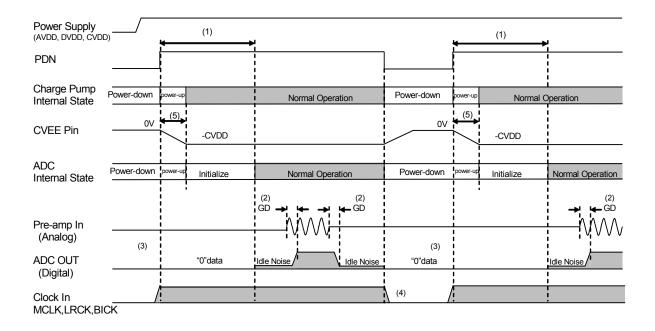

| 21  | PDN      | Ι   | Power Down Mode & Reset Pin<br>"H": Power up, "L": Power down & Reset                                                                                                                                                                                                                                                    |

|     |          |     | The AK5367A must be reset once upon power-up.                                                                                                                                                                                                                                                                            |

| 22  | SDA      | I/O | Control Data Input / Output Pin in I <sup>2</sup> C Control                                                                                                                                                                                                                                                              |

| 23  | SCL      | I   | Control Data Clock Pin in I <sup>2</sup> C Control                                                                                                                                                                                                                                                                       |

| 24  | SDTO     | 0   | Audio Serial Data Output Pin<br>"L" Output at Power-down mode.                                                                                                                                                                                                                                                           |

| 25  | BICK     | I/O | Audio Serial Data Clock Pin<br>"L" Output in Master Mode at PWN bit= "0".                                                                                                                                                                                                                                                |

| 26  | MCLK     | I   | Master Clock Input Pin                                                                                                                                                                                                                                                                                                   |

| No. | Pin Name | I/O | Function                                                        |

|-----|----------|-----|-----------------------------------------------------------------|

| 27  | LRCK     | I/O | Channel Clock Pin<br>"L" Output in Master Mode at PWN bit= "0". |

| 28  | DVDD     | -   | Digital Power Supply Pin, 3.0~ 3.6V                             |

| 29  | VSS1     | -   | Analog Ground Pin                                               |

| 30  | AVDD     | -   | Analog Power Supply Pin, 4.5 ~ 5.5V                             |

Note: All input pins except analog input pins (RISEL, LISEL, LIN1-4, RIN1-4) must not be left floating.

## Handling of Unused Pin

The unused input pins should be processed appropriately as below.

| C | lassification | Pin Name                                           | Setting                  |

|---|---------------|----------------------------------------------------|--------------------------|

|   | Analog        | LIN1-4,RIN1-4,LISEL,RISEL<br>LOPIN,LOUT,ROPIN,ROUT | These pins must be open. |

|                      | ABSOLUTE MAXI                       | MUM RATINGS |      |          |       |

|----------------------|-------------------------------------|-------------|------|----------|-------|

| (VSS1=VSS2=0V;       | Note 1, Note 2)                     |             |      |          |       |

| Parameter            |                                     | Symbol      | min  | max      | Units |

| Power Supplies:      | Analog                              | AVDD        | -0.3 | 6.0      | V     |

|                      | Digital                             | DVDD        | -0.3 | 6.0      | V     |

|                      | Charge Pump                         | CVDD        | -0.3 | 4.0      | V     |

| Input Current, Any   | Pin Except Supplies                 | IIN         | -    | ±10      | mA    |

| Analog Input Volta   | ge(LISEL,RISEL,LIN1-4, RIN1-4 pins) | VINA        | -0.3 | AVDD+0.3 | V     |

| Digital Input Voltag | ge (Note 3)                         | VIND        | -0.3 | DVDD+0.3 | V     |

| Ambient Temperatu    | re (Powered applied)                | Та          | -20  | 85       | °C    |

| Storage Temperatur   | e                                   | Tstg        | -65  | 150      | °C    |

Note 1. All voltages with respect to ground.

Note 2. VSS1 and VSS2 must be connected to the same analog ground plane.

Note 3. PDN, SCL, SDA, MCLK, BICK, LRCK pins

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

|                | RECOMMENDED OPERATING CONDITIONS |              |      |     |      |       |  |  |  |  |

|----------------|----------------------------------|--------------|------|-----|------|-------|--|--|--|--|

| (VSS1=VSS2=0V  | (VSS1=VSS2=0V; Note 1)           |              |      |     |      |       |  |  |  |  |

| Parameter      |                                  | Symbol       | min  | typ | max  | Units |  |  |  |  |

|                | Analog                           | AVDD         | 4.5  | 5.0 | 5.5  | V     |  |  |  |  |

| Power Supplies | Digital                          | DVDD         | 3.0  | 3.3 | 3.6  | V     |  |  |  |  |

| (Note 4)       | Charge Pump                      | CVDD         | 3.0  | 3.3 | 3.6  | V     |  |  |  |  |

|                | DVDD-CVDD                        | $\Delta VDD$ | -0.3 | 0   | +0.3 | V     |  |  |  |  |

Note 4. The power up sequence between AVDD, DVDD and CVDD is not critical.

In slave mode, the AK5367A must be power up at the PDN pin = "L".

In master mode, the AK5367A must be power up at the PDN pin = "L", or when DVDD is powered up, MCLK clock must input and the AK5367A must be reset by the PDN pin="L". The internal register data is unknown until PDN pin="L". The power on/off sequence between AVDD, DVDD and CVDD is not critical, however when DVDD is powered off, all digital input pins must be left floating or held to VSS.

The power off is means that AVDD, CVDD and DVDD are floating or short to VSS.

WARNING: AKEMD assumes no responsibility for the usage beyond the conditions in this datasheet.

#### ANALOG CHARACTERISTICS

(Ta=25°C; AVDD=5.0V, DVDD=CVDD=3.3V; VSS1=VSS2=0V; fs=48kHz,96kHz; BICK=64fs;

Signal Frequency=1kHz; 24bit Data; Measurement frequency=20Hz ~ 20kHz at fs=48kHz, 40Hz ~ 40kHz at fs=96kHz; unless otherwise specified)

| Parameter                            |              | min | typ  | max | Units  |

|--------------------------------------|--------------|-----|------|-----|--------|

| Pre-Amp Characteristics:             | ·            |     |      |     |        |

| Feedback Resistance                  |              | 10  |      | 50  | kΩ     |

| S/(N+D)                              | (Note 5)     | -   | 100  |     | dB     |

| S/N (A-weighted)                     | (Note 5)     | -   | 108  |     | dB     |

| Load Resistance R <sub>L</sub>       | (Note 6)     | 15  |      |     | kΩ     |

| Load Capacitance C <sub>L</sub>      | (Note 6)     |     |      | 20  | pF     |

| ADC Analog Input Characteristics: (N | lote 7)      |     |      |     |        |

| Resolution                           |              |     |      | 24  | Bits   |

| Input Voltage                        | (Note 8)     | 2.7 | 3.0  | 3.3 | Vpp    |

| S/(N+D) fs=48kHz                     | -1dBFS       | 82  | 90   |     | dB     |

| BW=20kHz                             | -60dBFS      | -   | 39   |     | dB     |

| fs=96kHz                             | -1dBFS       | -   | 90   |     | dB     |

| BW=40kHz                             | -60dBFS      | -   | 37   |     | dB     |

| DR (-60dBFS, A-weighted)             |              | 94  | 102  |     | dB     |

| S/N (A-weighted)                     |              | 94  | 102  |     | dB     |

| Interchannel Isolation (fs=48kHz)    | (Note 9)     | 85  | 96   |     | dB     |

| Interchannel Gain Mismatch           |              |     | 0.1  | 0.5 | dB     |

| Gain Drift                           |              |     | 100  | -   | ppm/°C |

| Power Supply Rejection               | (Note 10)    | -   | 50   |     | dB     |

| Power Supplies                       |              |     |      |     |        |

| Power Supply Current                 |              |     |      |     |        |

| Normal Operation (PDN pin = "H"      | ")           |     |      |     |        |

| AVDD                                 | ,            |     | 15.5 | 23  | mA     |

| CVDD                                 |              |     | 2.5  | 4   | mA     |

| DVDD (fs=48kHz                       |              |     | 2    | 3   | mA     |

| DVDD (fs=96kHz                       | ,            |     | 4    | 6   | mA     |

|                                      | ,            |     | 4    | 0   | IIIA   |

| Power down mode (PDN pin = "L'       | ') (Note 11) |     | 10   | 100 |        |

| AVDD+DVDD                            |              |     | 10   | 100 | μA     |

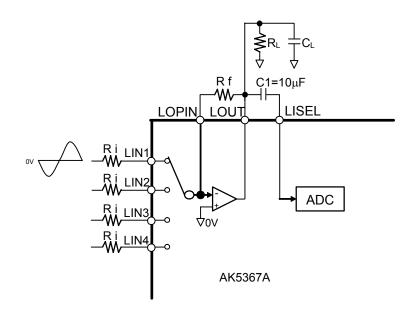

Note 5. This value is measured at LOUT and ROUT pins using Ri= 47k $\Omega$ , Rf= 24 k $\Omega$  when the input signal voltage is 2Vrms.

Note 6. This value of  $R_L$  and  $C_L$  are load resistance and capacitance that the LOUT and ROUT pins can drive.  $R_L$  does not include the feedback resistor (Rf) and the input impedance of the LISEL/RISEL pins. The value of  $C_L$  does not include the internal impedance of the AK5367A.

Note 7. This value is measured via the following path. Pre-Amp  $\rightarrow$  ADC.(Ri= 47k\Omega, Rf= 24 k\Omega)

Note 8. Input voltage to LISEL and RISEL pins is proportional to AVDD voltage. typ.  $Vin = 0.6 \times AVDD$  (Vpp) Note 9. 93dB(typ.) at fs=96kHz.

Note 10. PSR is applied to AVDD and DVDD with 1kHz, 50mVpp Sine wave.

Note 11. All digital input pins are held DVDD or VSS2.

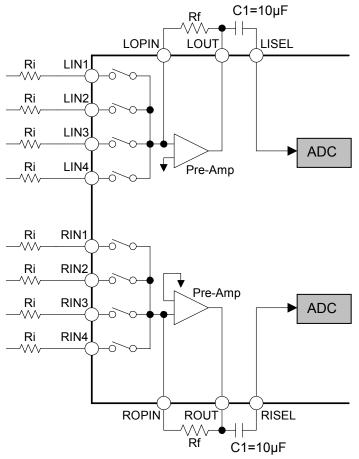

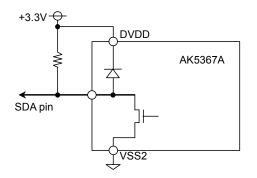

Figure 2. Pre-Amp Circuit

| FILTER | CHAR | ACTERI | STICS | (fs=48kHz) |

|--------|------|--------|-------|------------|

|--------|------|--------|-------|------------|

| (Ta=-20 ~ 85°C; AVDD=4.5 ~ 5.5V; DVDD=CVDD=3.0 ~ 3.6V) |               |           |             |     |      |       |       |  |  |

|--------------------------------------------------------|---------------|-----------|-------------|-----|------|-------|-------|--|--|

| Parameter                                              |               |           | Symbol      | min | typ  | max   | Units |  |  |

| ADC Digital Filter                                     | r (Decimation | LPF):     |             |     |      |       |       |  |  |

| Passband                                               | (Note 12)     | ±0.1dB    | PB          | 0   |      | 18.9  | kHz   |  |  |

|                                                        |               | -0.2dB    |             | -   | 20.0 | -     | kHz   |  |  |

|                                                        |               | -3.0dB    |             | -   | 23.0 | -     | kHz   |  |  |

| Stopband                                               |               |           | SB          | 28  |      |       | kHz   |  |  |

| Passband Ripple                                        |               |           | PR          |     |      | ±0.04 | dB    |  |  |

| Stopband Attenuati                                     | ion           |           | SA          | 68  |      |       | dB    |  |  |

| Group Delay Disto                                      | rtion         |           | $\Delta GD$ |     | 0    |       | μs    |  |  |

| Group Delay                                            |               | (Note 13) | GD          |     | 20   |       | 1/fs  |  |  |

| ADC Digital Filter                                     | r (HPF):      |           |             |     |      |       |       |  |  |

| Frequency Response                                     | se (Note 12)  | -3dB      | FR          |     | 1.0  |       | Hz    |  |  |

|                                                        |               | -0.1dB    |             |     | 6.5  |       | Hz    |  |  |

|                  |                | FILTER (  | CHARACTER     | ISTICS (fs= | :96kHz) |       |       |

|------------------|----------------|-----------|---------------|-------------|---------|-------|-------|

| (Ta=-20 ~ 85°C;  | AVDD=4.5 ~ 5   | .5V; DVDD | =CVDD=3.0 ~ ( | 3.6V)       |         |       |       |

| Parameter        |                |           | Symbol        | min         | typ     | max   | Units |

| ADC Digital Filt | er (Decimation | LPF):     |               |             |         |       |       |

| Passband         | (Note 12)      | ±0.1dB    | PB            | 0           |         | 37.8  | kHz   |

|                  |                | -0.2dB    |               | -           | 40.0    | -     | kHz   |

|                  |                | -3.0dB    |               | -           | 46.0    | -     | kHz   |

| Stopband         |                |           | SB            | 56          |         |       | kHz   |

| Passband Ripple  |                |           | PR            |             |         | ±0.04 | dB    |

| Stopband Attenua | tion           |           | SA            | 68          |         |       | dB    |

| Group Delay Dist | ortion         |           | $\Delta GD$   |             | 0       |       | μs    |

| Group Delay      |                | (Note 13) | GD            |             | 20      |       | 1/fs  |

| ADC Digital Filt | er (HPF):      |           |               |             |         |       |       |

| Frequency Respon | nse (Note 12)  | -3dB      | FR            |             | 2.0     |       | Hz    |

|                  |                | -0.1dB    |               |             | 13.0    |       | Hz    |

Note 12. The passband and stopband frequencies scale with fs. For example, PB= 18.9kHz@±0.1dB is 0.39375 x fs, (fs=48kHz).

Note 13. The calculated delay time induced by digital filtering. This time is from the input of an analog signal to the setting of 24bit data both channels to the ADC output register for ADC.

| DC CHARACTERISTICS         |                                                          |        |          |     |         |       |  |  |  |

|----------------------------|----------------------------------------------------------|--------|----------|-----|---------|-------|--|--|--|

| (Ta=-20°C ~ 85°C; AVDD=4.5 | (Ta=-20°C ~ 85°C; AVDD=4.5 ~ 5.5V; DVDD=CVDD=3.0 ~ 3.6V) |        |          |     |         |       |  |  |  |

| Parameter                  |                                                          | Symbol | min      | typ | max     | Units |  |  |  |

| High-Level Input Voltage   |                                                          | VIH    | 70%DVDD  | -   | -       | V     |  |  |  |

| Low-Level Input Voltage    |                                                          | VIL    | -        | -   | 30%DVDD | V     |  |  |  |

| High-Level Output Voltage  | (Iout=-1mA)                                              | VOH    | DVDD-0.5 | -   | -       | V     |  |  |  |

| Low-Level Output Voltage   |                                                          |        |          |     |         |       |  |  |  |

| (Except SDA)               | pin: Iout=1mA)                                           | VOL    | -        | -   | 0.5     | V     |  |  |  |

| (SDA pin: Iou              | t=3mA)                                                   | VOL    | -        | -   | 0.4     | V     |  |  |  |

| Input Leakage Current      |                                                          | Iin    | -        | -   | ±10     | μΑ    |  |  |  |

AKM

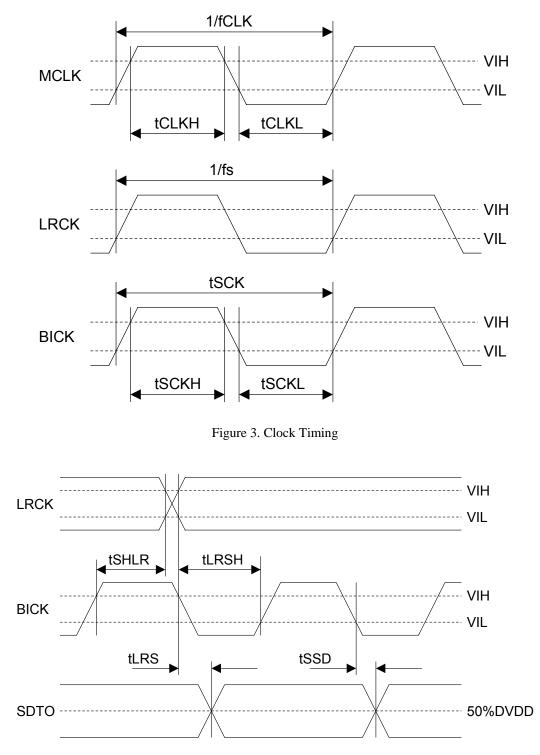

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | SWITCHIN                     | G CHARAC      | TERISTICS       |      |        |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------|---------------|-----------------|------|--------|-------|

| Master Clock Timing<br>512b, 256ik Frequency    (CLK    8.192    24.576    MHz      Pulse Width Low    (CLKL    16    ns    ns      Pulse Width Low    (CLKH    16    ns    ns      Pulse Width High    (CLKL    10.5    ns    ns      Pulse Width High    (CLKL    10.5    ns    ns      Pulse Width High    (CLKH    10.5    ns    ns      Duty Cycle    Slave mode    45    50    %      Audio Interface Timing    10    10    ns    ns      Slave mode    (SCKL    65    ns    ns      BICK Period    (SCKL    65    ns    ns      BICK "1" to SDTO (MSB) (Except 1 <sup>2</sup> S mode)    (LRS    30    ns    ns      BICK "4" to SDTO (MSB) (Except 1 <sup>2</sup> S mode)    (LSD    50    %    Master mode    12      BICK "4" to SDTO    (SSD    -20    35    ns    ns      BICK V-4" to SDTO    (SSD    -20    35    ns      BICK Trequency    fSCL    -    400    kHz      BICK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (Ta=-20°C ~ 85°C; AVDD          | =4.5 ~ 5.5V; DVDD=CV         | VDD=3.0 ~ 3.0 | $5V; C_L=20pF)$ |      |        |       |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Parameter                       |                              | Symbol        | min             | typ  | max    | Units |

| Pulse Width LowtCLKL16nsPulse Width LowtCLKH16ns768is, 384is FrequencyfCLK12.28836.864Pulse Width HightCLKH10.5nsPulse Width HightCLKH10.5nsLRCK Frequencyfs3296Master mode4550%Audio Interface Timing50%Audio Interface TimingtSCK160nsBICK PeriodtSCK160nsBICK PeriodtSCKL65nsPulse Width HightSCKL65nsBICK 42r to SDTO (MSB) (Except 12 Smode)tLRS35nsBICK +2r to SDTO (MSB) (Except 12 Smode)tLRS35nsBICK +2r to SDTO (MSB) (Except 12 Smode)tLRS50%BICK +2r to SDTOfSCK64fsHzBICK +2r to SDTOtSSD-2035nsStart Condition Hold TimetBSR-2020nsBICK +2r to SDTOfSCL-400kHzBICK +2r to SDTOtBSD-2035nsControl Interface Timing (I <sup>2</sup> C Bus mode):tBSD-2035nsClock High TimetLOW1.3-µsStart Condition Hold TimetHD:STA0.6-µsSDA Hold Time from SCL Raling (Note 15)tHIGH0.6-µsStart Condition Hold TimetHD:STA0.6-µsStart Condition Hold TimetHD:STA <td>Master Clock Timing</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Master Clock Timing             |                              |               |                 |      |        |       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 512fs, 256fs Frequency          |                              | fCLK          | 8.192           |      | 24.576 | MHz   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pulse Width Low                 |                              | tCLKL         | 16              |      |        | ns    |

| Pulse Width LowtCLKL10.5nsPulse Width HightCLKH10.5IRC K Frequencyfs3296kHzDuty CycleSlave mode4550%Audio Interface TimingColspan="2">Colspan="2">Colspan="2">Colspan="2">Colspan="2">Colspan="2">Colspan="2">Colspan="2">Colspan="2">Nave modeSlave mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pulse Width High                |                              | tCLKH         | 16              |      |        | ns    |

| $ \begin{array}{c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c } \hline \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 768fs, 384fs Frequency          |                              | fCLK          | 12.288          |      | 36.864 | MHz   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pulse Width Low                 |                              | tCLKL         | 10.5            |      |        | ns    |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Pulse Width High                |                              | tCLKH         | 10.5            |      |        | ns    |

| $\begin{tabular}{ c c c c c c } \hline Duty Cycle & Slave mode & 45 & 55 & \% \\ \hline Master mode & 50 & 96 \\ \hline Slave mode & 50 & 96 \\ \hline Slave mode & 50 & 96 \\ \hline BICK Period & Slave mode & 50 & 96 \\ \hline BICK Pulse Width Low & 15CKL & 65 & 98 \\ \hline BICK Pulse Width High & 15CKH & 65 & 98 \\ \hline Pulse Width High & 15CKH & 65 & 98 \\ \hline LRCK Edge to BICK "\?" (Note 14) & 1LRSH & 30 & 98 \\ \hline LRCK to SDTO (MSB) (Except 12S mode) & 1LRS & 35 & 98 \\ \hline BICK "\" to LRCK Edge & (Note 14) & 1SHLR & 30 & 98 \\ \hline BICK "\" to LRCK Edge & (Note 14) & 1SHLR & 30 & 98 \\ \hline BICK "\" to LRCK Edge & (Note 14) & 1SKD & 355 & 98 \\ \hline Master mode & 50 & 355 & 98 \\ \hline Master mode & 50 & 98 \\ \hline BICK "\" to LRCK I C SDTO & 1SSD & 98 \\ \hline BICK "\ U'' to LRCK & 10RCK & 10RCK & 10RCK & 50 & 98 \\ \hline BICK "\ U'' to LRCK & 10RCK & 1$ | LRCK Frequency                  |                              | fs            | 32              |      | 96     | kHz   |

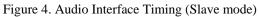

| Audio Interface TimingSo%Slave modetSCK160nsBICK PeriodtSCK160nsBICK Pulse Width LowtSCKL65nsPulse Width HightSCKL65nsLRCK Edge to BICK "↑" (Note 14)tLRSH30nsBICK *↑" to LRCK Edge (Note 14)tSHLR30nsBICK *↑" to SDTO (MSB) (Except 12 mode)tLRS35nsBICK *↓" to SDTO (MSB) (Except 12 mode)tLRS35nsBICK *↓" to SDTOtSSD-35nsBICK *↓" to SDTOtSSD-35nsBICK *↓" to SDTOtSSD-2035nsBICK *↓" to SDTOtSSD-2035nsBICK *↓" to SDTOtSSD-2035nsCottor Interface Timing (I <sup>2</sup> C Bus mode):tHD: STA0.6- $\mu$ sCock Low TimeLOW1.3- $\mu$ sClock Low TimeLOW1.3- $\mu$ sClock Low Time for SCL RisingtHD:DAT0- $\mu$ sStart Condition HSDA and SCL LinestH-0.3 $\mu$ sStart Time of Both SDA and SCL LinestF-0.3 $\mu$ sFall Time of Both SDA and SCL LinestF-0.3 $\mu$ sStup Time for Stop ConditiontSU:STO0.6- $\mu$ sStup Time for Stop ConditiontSU:STO0.6- $\mu$ sStup Time for Stop ConditiontSU:STO0.6- $\mu$ s<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 | Slave mode                   |               | 45              |      | 55     | %     |

| Slave mode<br>BICK PeriodtSCK160nsBICK Pulse Width LowtSCKL65nsPulse Width HightSCKH65nsLRCK Edge to BICK " $\uparrow$ " (Note 14)tLRSH30nsBICK " $\uparrow$ " to LRCK Edge(Note 14)tSHLR30nsLRCK to SDTO (MSB) (Except I <sup>2</sup> S mode)tLRS35nsBICK " $\downarrow$ " to SDTOtSSD35nsMaster mode111BICK " $\downarrow$ " to LRCKtMSLR-2020BICK " $\downarrow$ " to LRCKtMSLR-2035BICK " $\downarrow$ " to LRCKtMSLR-2035BICK " $\downarrow$ " to SDTOtSSD-2035Cottrol Interface Timing (I <sup>2</sup> C Bus mode):tSCL-Cottrol Interface Timing (I <sup>2</sup> C Bus mode):tBUF1.3Cottrol Interface Timing (I <sup>2</sup> C Bus mode):Up to the theorem of th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                 | Master mode                  |               |                 | 50   |        | %     |

| Slave mode<br>BICK PeriodtSCK160nsBICK Pulse Width LowtSCKL65nsPulse Width HightSCKH65nsLRCK Edge to BICK " $\uparrow$ " (Note 14)tLRSH30nsBICK " $\uparrow$ " to LRCK Edge(Note 14)tSHLR30nsLRCK to SDTO (MSB) (Except I <sup>2</sup> S mode)tLRS35nsBICK " $\downarrow$ " to SDTOtSSD35nsMaster mode111BICK " $\downarrow$ " to LRCKtMSLR-2020BICK " $\downarrow$ " to LRCKtMSLR-2035BICK " $\downarrow$ " to LRCKtMSLR-2035BICK " $\downarrow$ " to SDTOtSSD-2035Cottrol Interface Timing (I <sup>2</sup> C Bus mode):tSCL-Cottrol Interface Timing (I <sup>2</sup> C Bus mode):tBUF1.3Cottrol Interface Timing (I <sup>2</sup> C Bus mode):Up to the theorem of th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Audio Interface Timing          |                              |               |                 |      |        |       |

| BICK PeriodtSCK160nsBICK Pulse Width LowtSCKL65nsPulse Width HightSCKH65nsLRCK Edge to BICK " $\uparrow$ " (Note 14)tLRSH30nsBICK " $\uparrow$ " to LRCK Edge (Note 14)tSHLR30nsBICK " $\uparrow$ " to LRCK Edge (Note 14)tSHLR30nsBICK " $\downarrow$ " to SDTOtLRS35nsBICK " $\downarrow$ " to SDTOtSSD35BICK " $\downarrow$ " to SDTOtSSD35BICK TequencyfSCK64fsHzBICK $\downarrow$ " to SDTOtSSD-2020BICK $\downarrow$ " to SDTOtSSD-2035BICK " $\downarrow$ " to SDTOtSSD-2035BICK " $\downarrow$ " to IRCKtMSLR-2020BICK " $\downarrow$ " to SDTOtSD-2035CottInterface Timing (I <sup>2</sup> C Bus mode):tBUF1.3-tSCL Clock FrequencyfSCL-400kHzBus Free Time Between TransmissionstBUF1.3- $\mu$ sStart Condition Hold TimetLOW1.3- $\mu$ sClock Low TimetLOW1.3- $\mu$ sClock High TimetHIGH0.6- $\mu$ sStart Condition SDA And SCL LinestR-0.3 $\mu$ sSetup Time for SDC And SCL LinestR-0.3 $\mu$ sFall Time of Both SDA and SCL LinestF-0.3 $\mu$ sSetup Time for SDC RomitiontSU:STO0.6- $\mu$ s </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |                              |               |                 |      |        |       |

| BICK Pulse Width LowtSCKL $65$ Image: state of the sta                                                                                                                                                                                     |                                 |                              | tSCK          | 160             |      |        | ns    |

| $\begin{tabular}{ c c c c } \hline Pulse Width High & tSCKH & 65 & t & ns \\ LRCK Edge to BICK "\^" (Note 14) & tLRSH & 30 & ns \\ BICK "\" to LRCK Edge (Note 14) & tSHLR & 30 & ns \\ BICK "\" to SDTO (MSB) (Except 1^2S mode) & tLRS & 35 & ns \\ BICK "\" to SDTO & tSSD & & 35 & ns \\ \hline Master mode & & 35 & ns \\ \hline Master mode & & & 1 & 1 \\ BICK Frequency & fSCK & 64fs & Hz \\ BICK Duty & dSCK & 50 & 0 & 96 \\ BICK "\'' to DRCK & tMSLR & -20 & 20 & ns \\ BICK "\'' to SDTO & tSSD & -20 & 35 & ns \\ \hline Master mode & & & 1 & 1 \\ \hline Master mode & & & & 1 & 1 \\ \hline Master mode & & & & & 1 \\ BICK Tequency & fSCK & 1 & 50 & & & & & & & & & & & & & & & & & $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                 | ow                           |               |                 |      |        | ns    |

| $\begin{tabular}{ c c c c c c } & LRCK Edge to BICK "\"'' (Note 14) tLRSH (1) tLRSH (1) tSHLR (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |                              |               |                 |      |        |       |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | •                            |               |                 |      |        | ns    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                               |                              | tSHLR         | 30              |      |        | ns    |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 | 0 ,                          | tLRS          |                 |      | 35     | ns    |

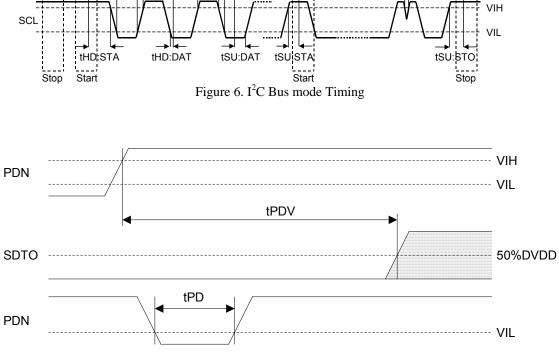

| BICK FrequencyfSCK64fsHzBICK DutydSCK50%BICK "↓" to LRCKtMSLR-2020nsBICK "↓" to SDTOtSSD-2035nsControl Interface Timing (I²C Bus mode):SCL Clock FrequencyfSCL-400kHzBus Free Time Between TransmissionstBUF1.3-µsStart Condition Hold TimetHD:STA0.6-µs(prior to first clock pulse)tHGH0.6-µsClock Low TimetLOW1.3-µsStart ConditiontSU:STA0.6-µsStart Condition Hold TimetHGH0.6-µs(prior to first clock pulse)t-µsStart ConditiontLOW1.3-µsStart ConditiontSU:STA0.6-µsSDA Hold Time for SCL Falling (Note 15)tHD:DAT0-µsSDA Setup Time for SCL RisingtR-0.3µsRise Time of Both SDA and SCL LinestF-0.3µsFall Time of Stop ConditiontSU:STO0.6-µsSetup Time for Stop ConditiontSU:STO0.6-µsPulse Width of Spike NoisetSP050nsSuppressed by Input Filterµs-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                 | , , ,                        | tSSD          |                 |      | 35     | ns    |

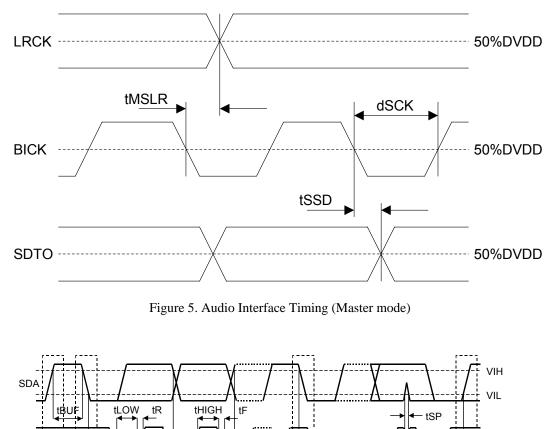

| BICK Duty<br>BICK " $\downarrow$ " to LRCK<br>BICK " $\downarrow$ " to SDTOdSCK50%BICK " $\downarrow$ " to SDTOtMSLR-2020nsBICK " $\downarrow$ " to SDTOtSSD-2035nsControl Interface Timing (I <sup>2</sup> C Bus mode):SCL Clock Frequency<br>Bus Free Time Between Transmissions<br>Start Condition Hold Time<br>(prior to first clock pulse)fSCL-400kHzClock Low Time<br>Clock High TimetHD:STA0.6- $\mu$ sClock High Time<br>SDA Hold Time from SCL Falling (Note 15)<br>SDA Setup Time from SCL Rising<br>Rise Time of Both SDA and SCL Lines<br>Fall Time of Stop Condition<br>Fall Time for Stop Condition<br>Suppressed by Input FiltertSC- $\mu$ sSetup Time for Stop Condition<br>Pulse Width of Spike Noise<br>Suppressed by Input FiltertSP0.6- $\mu$ sSuppressed by Input FiltertSU:STO0.6- $\mu$ s $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Master mode                     |                              |               |                 |      |        |       |

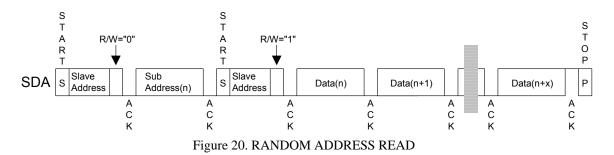

| BICK DutydSCK50%BICK " $\downarrow$ " to LRCKtMSLR-2020nsBICK " $\downarrow$ " to SDTOtSSD-2035nsControl Interface Timing (I <sup>2</sup> C Bus mode):SCL Clock FrequencyfSCL-400kHzBus Free Time Between TransmissionstBUF1.3- $\mu$ sStart Condition Hold TimetHD:STA0.6- $\mu$ s(prior to first clock pulse)tLOW1.3- $\mu$ sClock High TimetLOW1.3- $\mu$ sStart Condition SDA Hold Time for Repeated Start ConditiontSU:STA0.6- $\mu$ sStart For Repeated Start ConditiontSU:STA0.6- $\mu$ sSDA Hold Time from SCL Falling (Note 15)tSU:DAT0- $\mu$ sStart Time of Both SDA and SCL LinestR-0.3 $\mu$ sFall Time of Stop ConditiontSU:STO0.6- $\mu$ sSetup Time for Stop ConditiontSU:STO0.6- $\mu$ sPulse Width of Spike NoisetSP050nsSuppressed by Input FiltertSP050ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>BICK</b> Frequency           |                              | fSCK          |                 | 64fs |        | Hz    |